16-Bit D-Type Transparent Latch with 3-State Outputs,74LVCN16373-Replace-74LVC16373ADGG-118.

74LVCN16373 74LVCN16373.pdf

74LVCN16373.pdf

74LVCN16373.pdf

74LVCN16373.pdfFEATURES

? 5V Tolerant Inputs/Outputs for Interfacing with

5V Logic

? Wide Supply Voltage Range: 1.2V to 3.6V

? CMOS Low Power Consumption

? Direct Interface with TTL Levels

? Inputs Accept Voltages up to 5.5V

? High-Impedance State When VCC = 0V

? -40℃ to +125℃ Operating Temperature Range

? Available in a Green TSSOP-48 Package

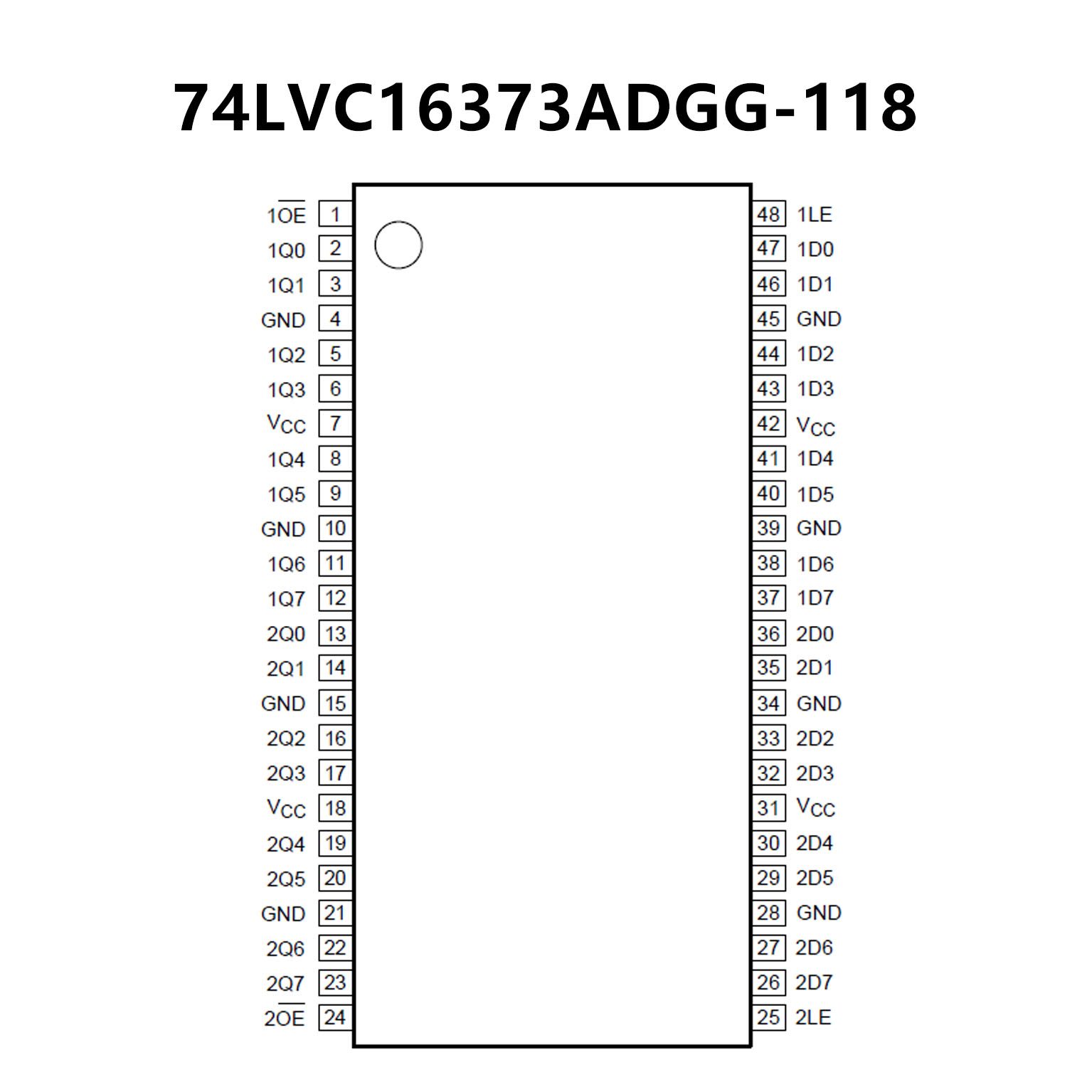

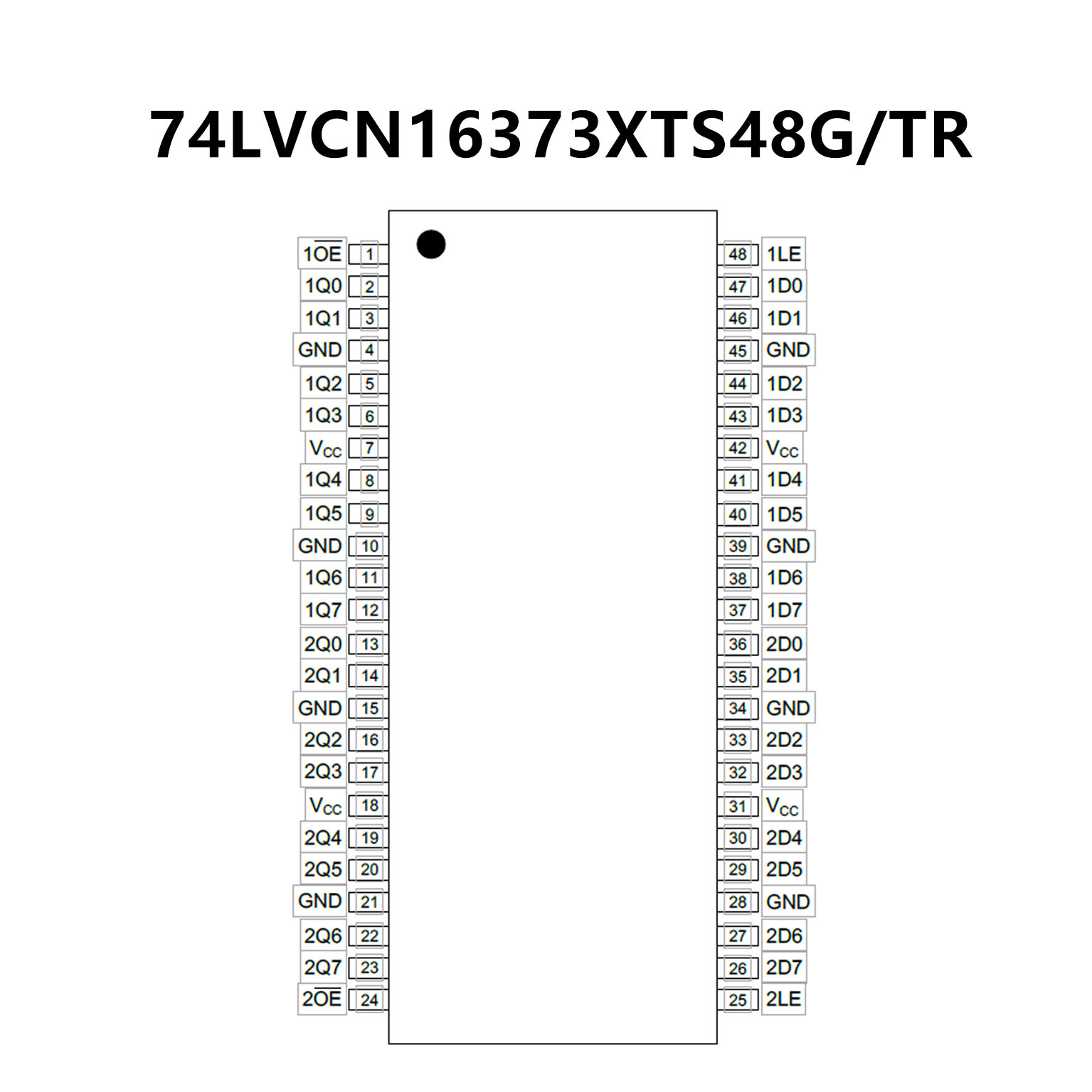

PIN CONFIGUTION

優勢替代

FEATURES

? Overvoltage tolerant inputs to 5.5 V

? Wide supply voltage range from 1.2 V to 3.6 V

? CMOS low power dissipation

? MULTIBYTE flow-through standard pinout architecture

? Multiple low inductance supply pins for minimum noise and ground bounce

? Direct interface with TTL levels

? All data inputs have bus hold (74LVCH16373A only)

? IOFF circuitry provides partial Power-down mode operation

? Complies with JEDEC standards:

? JESD8-7A (1.65 V to 1.95 V)

? JESD8-5A (2.3 V to 2.7 V)

? JESD8-C/JESD36 (2.7 V to 3.6 V)

? ESD protection:

? HBM JESD22-A114F exceeds 2000 V

? MM JESD22-A115-B exceeds 200 V

? CDM ANSI/ESDA/Jedec JS-002 exceeds 1000 V

? Specified from -40 °C to +85 °C and -40 °C to +125 °C

PIN CONFIGUTION